# How to evaluate your next IP-Core in the Cloud

#### Lorenz Kolb

Sr. Member Technical Staff Missing Link Electronics

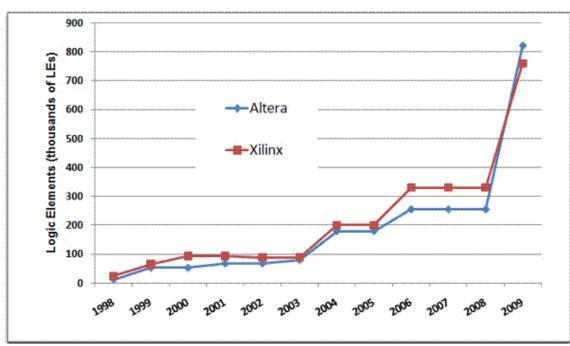

### **FPGA** design complexity

- Complexity of FPGAs rapidly growing

- Complexity of FPGA designs is directly proportional

Courtesy: Xilinx, Inc.

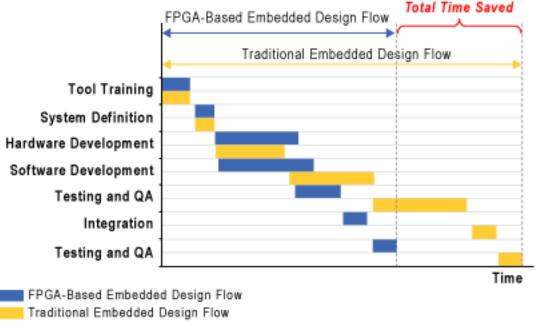

### **Projected development times**

Development times projected to be less compared to traditional approaches

Courtesy: Altera, Inc.

#### **IP-Cores filling the gap**

- Pre-built building blocks to bridge the gap

- Standard interfaces

- FPGA internal bus interface

- Software interface

- Tool integration

- Reference designs

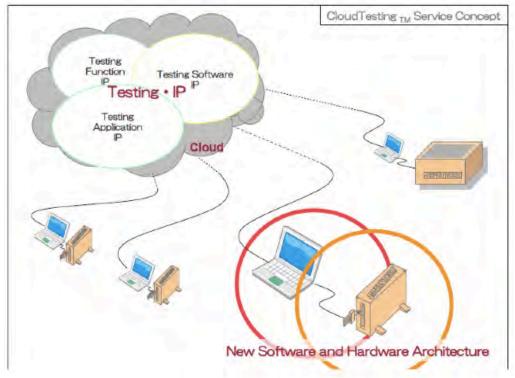

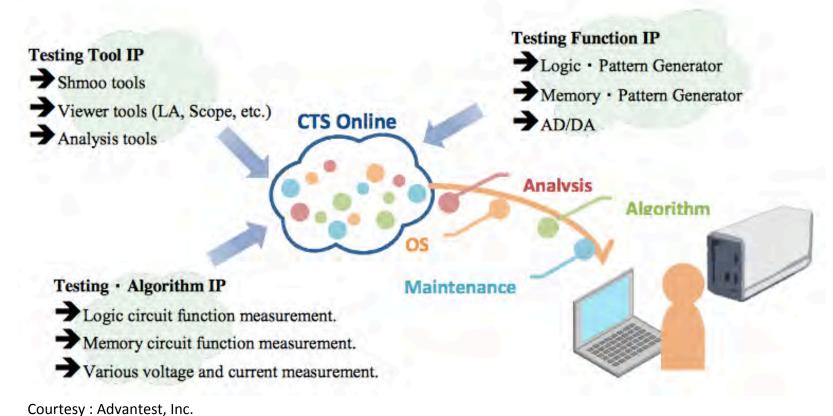

#### **State of the Art: Cloud Testing Service**

- Introduced by Advantest

- Testing for Hardware components

- Moves test program component development into the cloud

- Tester itself as a physical box on the own desk

Courtesy: Advantest, Inc.

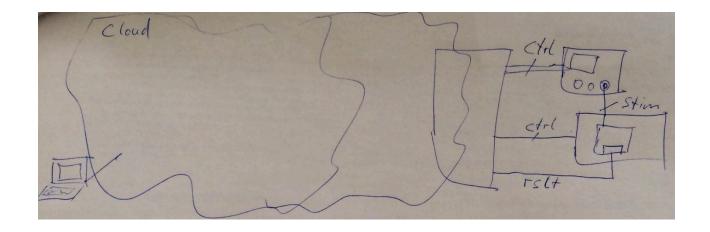

### **State of the Art: Cloud Testing Service (Concept)**

### **New Challenge: Finding the right IP-Core**

- Make or buy

- Binary vs. source code licenses

- Maintainability

- The legal challenges

- Evaluation licenses

- Qualifying a vendor

- The evaluation phase

- Does the IP-Core work?

- How to test Blackbox

#### **Blackbox IP evaluation**

- Resources

- Price

- Functionality

- Reference design

- Stimulus

- Verification

- Own test equipment needed

- Own test setup/scripts needed

- Acceptance

- Ability to integrate in own solution

### **IP-Core cloud testing concept**

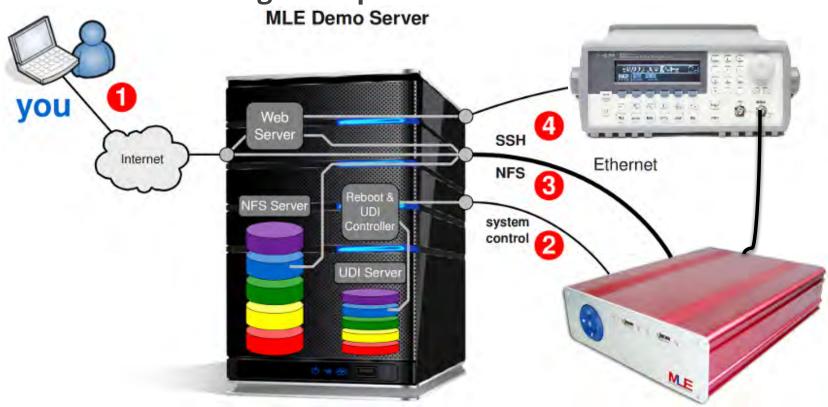

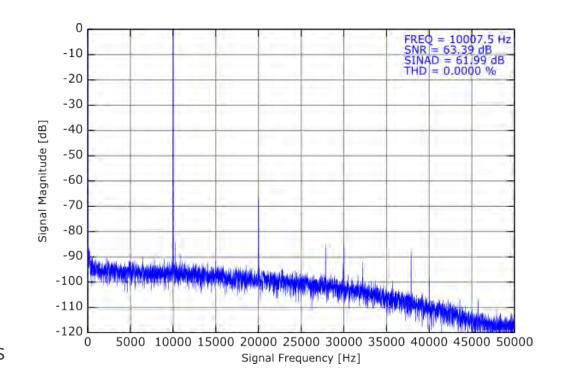

#### **Example: MLE SoftADC IP (IP test setup)**

- Input

- Selectable GPIB scripts for Agilent Arbitrary Function Generator

- Output:

- Results as CSV

- Results as Plot

- Future

- Input

- WAV files

- OutputOscilloscope Results

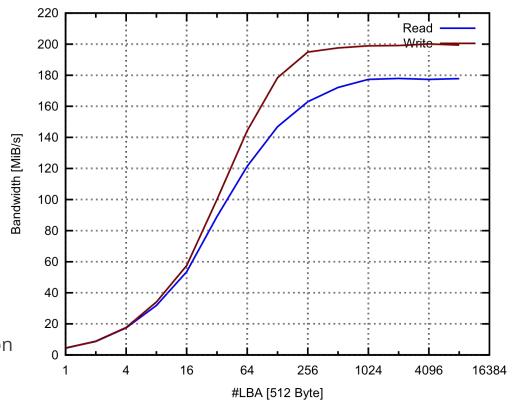

# **Example 2: Zynq SATA Storage Extension (IP test setup)**

- Input

- FIO test script

- Output:

- Results as CSV

- Results as Plot

- Future

- Input

- Test modes

- Output

- Protocol Analyzer Information

- Oscilloscope Results

#### **Contact Information**

Missing Link Electronics GmbH Industriestrasse 4 89231 Neu-Ulm Phone DE: +49 (731) 141149-0

Missing Link Electronics, Inc. 15711 E Alta Vista San Jose, CA 95127 Phone US: +1 (408) 457-0700

www.MLEcorp.com

#### **Getting started example**

- Only actuator, no analyzing

- Android/iPhone app available

Live Online

Evaluation

Introduction

Select a Tutorial

Basic Tutorial

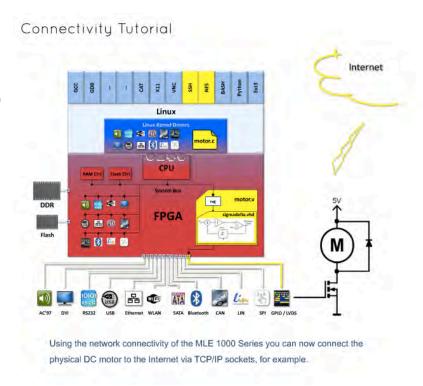

Connectivity Tutorial

System Tutorial

Connectivity Tutorial

Connectivity Tutorial

Conclusion

SATA Tutorial

BeMicro Tutorial

ML507 USB Demo

The Live Online Evaluation (LOE) is a web-based user experience that allows you to quickly evaluate the MLE technology. For that we have set up a growing list of guided tutorials.

ML605 Linux Demo

# Why IPs?

✓ | Standardized IP is critical to. assembling a working system-onchip particularly when it comes to specialized circuit functions. IP vendors can assist the designer by insuring that a given IP block not only conforms to standards, but also has been thoroughly tested and verified to produce the required functions. The designer can then concentrate on the custom aspects of the design that make it unique in the market.

Source: Alentor Braphics

#### **Blackbox IP evaluation in the cloud**

#### **FPGA** design complexity

- Complexity of FPGAs rapidly growing

- Complexity of FPGA designs is directly proportional

Courtesy (e.g.): http://www.soccentral.com/results.asp? CatID=488&EntryID=30730