# TCP/IP

SNIA Storage Developers Conference, Sept. 16-18, 2024 in Santa Clara, CA

The Storage Developers Conference (SDC) 2024 of SNIA, the Storage and Networking Industry Alliance, will be held Sept. 16-18 in Santa Clara, CA. There, MLE will present “Complementing TCP with…

TCP/IP for Real-Time Embedded Systems: The Good, the Bad and the Ugly

Presentation at the Embedded World 2024, Nuremberg, Germany, Apr. 9, 2024 Embedded systems such as in-vehicle networks, modern factory automation or autonomous robots, for example, are undergoing a major shift:…

MLE Updates TCP/UDP/IP Network Protocol Accelerator Platform

MLE has released an update, Version 2.3.3., of its Network Protocol Acceleration Platform (NPAP). This update is fixing minor issues with AXI4 bus scheduler fairness, IP Core packaging for AMD/Xilinx…

Shift-Left Your FPGA Design Project with FPGA Full System Stacks from Trenz Electronic and MLE

Visit us at Embedded World 2024! The Embedded World 2024 tradeshow will be held April 9-11 in Nuremberg, Germany. Here, partners Trenz Electronic and MLE will present solutions for you…

MLE Presents “TCP/IP for Real-Time Embedded Systems: The Good, the Bad and the Ugly” at Embedded World 2024

The Embedded World Conference 2024 will be held April 9-11 in Nuremberg, Germany. There, MLE will present “TCP/IP for Real-Time Embedded Systems: The Good, the Bad and the Ugly.” Embedded…

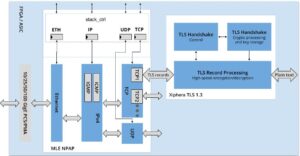

Xiphera and Missing Link Electronics Announce a Partnership for Encrypted Network Accelerator Solutions (ENAS)

With the new Encrypted Network Accelerator Solutions brought to the market, Xiphera and MLE offer a cryptographically secure and reliable connection between devices over TCP/IP. Xiphera, Ltd, designing hardware-based security…

MLE Participates at AMD/Xilinx Security Working Group 2023

The AMD-Xilinx Security Working Group takes place face-to-face in Munich, Germany, from December 5-6, 2023. Presentations include the latest security features in Versal ACAP and updates for the product roadmap.…

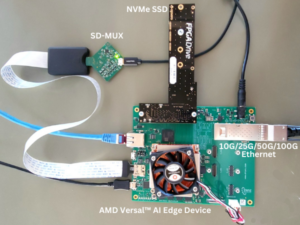

MLE and Trenz Verify the AMD/Xilinx Versal™ AI Edge Device and Accelerate Networking and Storage with 10G/25G/50G/100G TCP/IP Core

MLE and Trenz Electronic, both Premier Members of the AMD Adaptive Computing Partner Program, have collaborated and worked on Trenz’s new TE0950 AMD/Xilinx Versal™ AI Edge Evalboard to provide an…

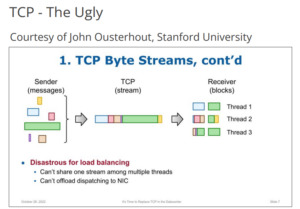

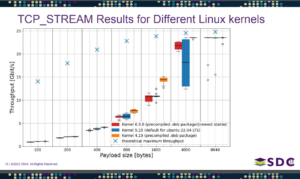

How Bad is TCP? (And What Are the Alternatives?)

Presentation at SNIA Storage Developers Conference, Fremont, CA, Sept. 18-21, 2023 Tail latencies in networking tend to worry us all, whether we implement distributed storage and compute or whether we…

Advantages of Using TCP for GigE Vision Devices

Allied Vision Technologies GmbH in Stadtroda, Germany, has worked with Missing Link Electronics (MLE) to integrate and to optimize MLE NPAP, the TCP/UDP/IP Full Accelerator Stack from Fraunhofer HHI, into…