Automotive Rapid Prototyping System (Auto/RPS)

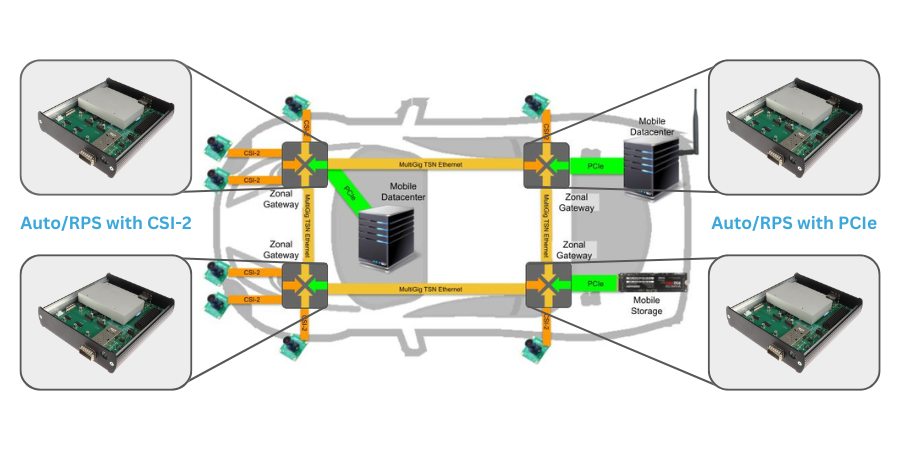

MLE provides an FPGA-based Rapid Prototyping System (RPS) catering to the specific needs of automotive engineers designing next-generation Zone Based Architectures.

MLE Auto/RPS enables automotive system engineers to design and to validate software-defined vehicle (SDV) functions along with MLE Auto/TSN in-vehicle networking.

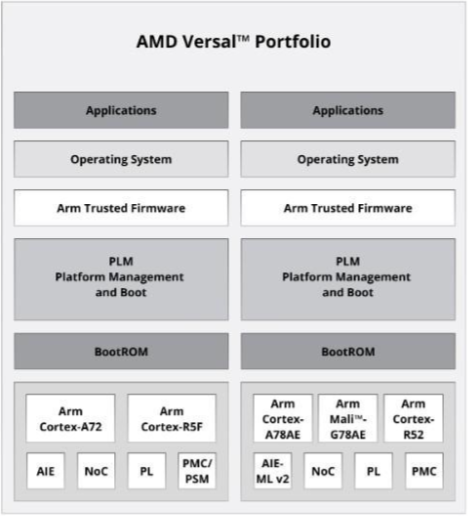

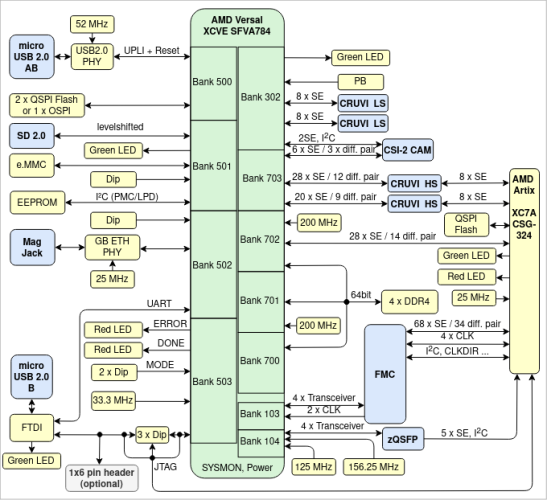

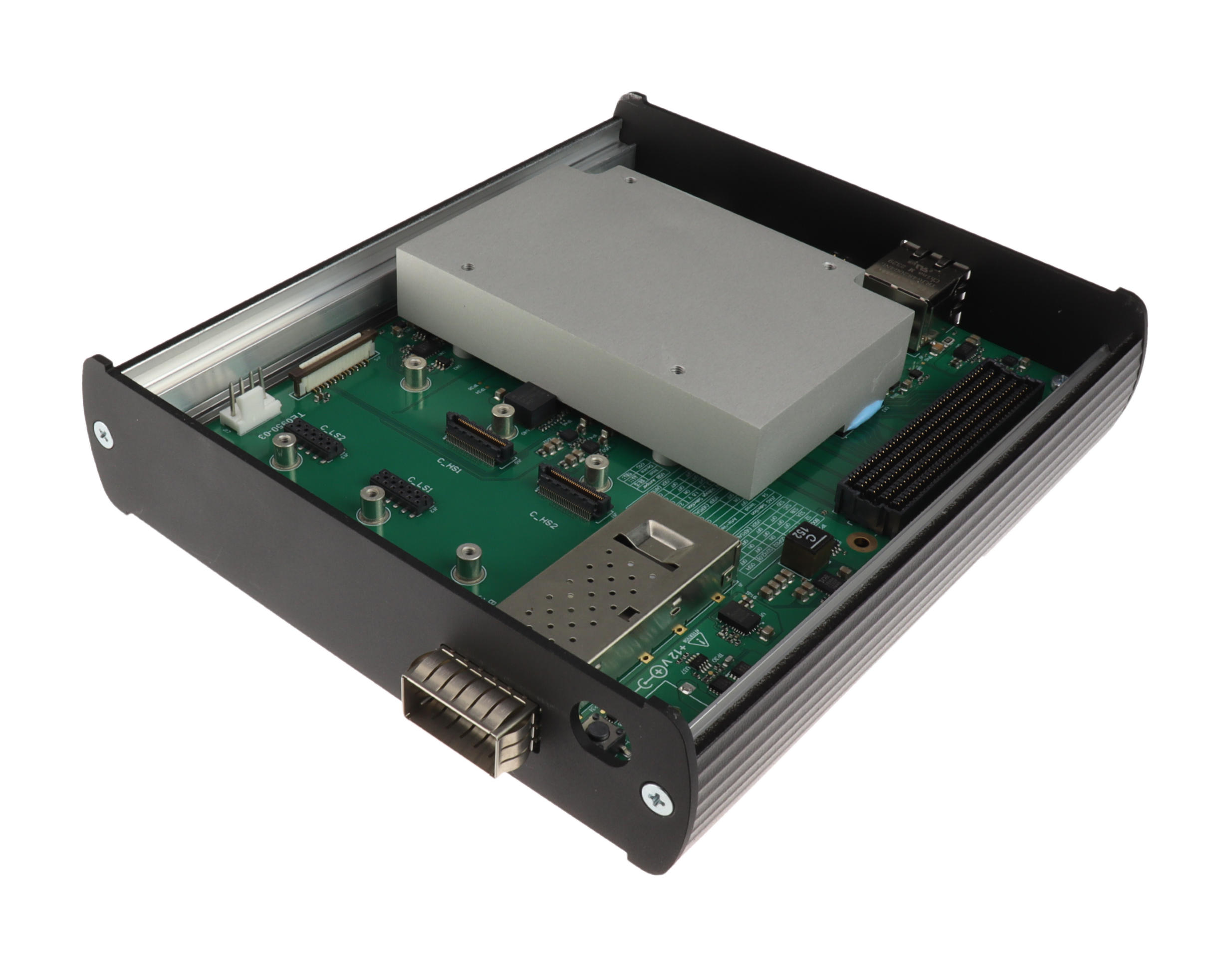

MLE Auto/RPS was designed as a shortcut into A-sample hardware development of Zonal Gateways / ECUs and implements an FPGA Full System Stack based on the Trenz Electronic TE0950-02 SoC-FPGA Development Kit featuring the AMD Versal AI Edge FPGA, and an automotive FPGA subsystem from MLE.

Edit Template

Features and Benefits

- Based on open standards and open-source software

- Support for multiple, different sensor inputs

- Backbone connectivity up to 100 Gbps

- Open-source real-time operating systems

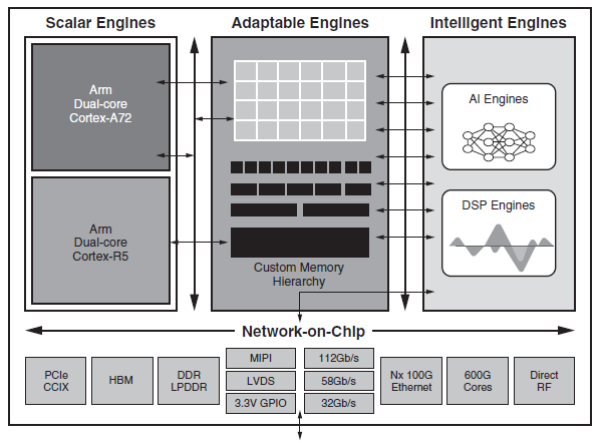

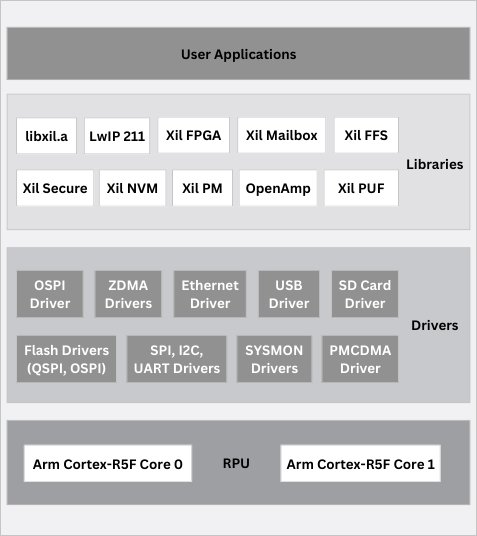

- Multi-core ARM processing system

- Flexible, adaptable FPGA design for implementing data acquisition and data preprocessing (DADP)

- Supports Secure OTA via ARM OP-TEE Trusted Execution Environment (optional)

IO Interfaces

- 12 V DC power supply

- 1 Gig Ethernet

- USB 2.0 for JTAG and console

- 2x ports for 25G Ethernet (up to 4 ports optional)

- MIPI CSI-2 x2 Camera Input (optional)

- GMSL (via optional adapter AD-GMSL2ETH-SL)

- Up to 2x CAN-FD (via CRUVI HS) (optional)

- Up to 2x CAN 2.0B (via CRUVI HS) (optional)

- PCIe 4.0 x4 NVMe M.2 SSD via Opsero FMC with 4x GTYP for (optional)

Processing Functionality

FPGA System Block Diagram

FPGA Development Kit

Auto/RPS-TE-0950-25G

- Hardware based on TE0950 AMD Versal™ AI Edge Evalboard from Trenz Electronic

- Features the AMD Versal™ AI Edge VE2302-1LSE

- FPGA Full System Stack for MLE Auto/TSN 2x25G

- Ubuntu 24.04 LTS for ARM

- Customized MLE Auto/TSN Linux kernel 6.6.10

- 12 VDC for lab and table top operation

Pricing and Availability

| Product Name | Deliverables | Example Pricing |

|---|---|---|

| Rapid Prototyping System (Base) AUTORPS-TE-0950-25G | FPGA Full System Stack for MLE Auto/TSN stack for 2x 25 GigE comprising hardware (FPGA board, power supply, active cooling, enclosure), system FPGA config (bitfile and rootfs). | $3,880,- per unit ( MOQ 2 units) |

| System FPGA Development Kit | AMD/Xilinx Vivado Design Project plus Commercial Single-Project-Use License delivered as encrypted netlists or RTL. | Please Inquire |

| Application-specific R&D Services | Advanced FPGA design services with access to acceleration experts from MLE. | $1,880.- per engineering day (or fixed price project fee) |

Please contact MLE for additional details on Auto/RPS products and services or other product and licensing options.

Edit Template

Documentation

Brochure

Application Note

Technical Document

News

Brochure

Application Note

Technical Document

News