Encrypted Network

Accelerator Solutions (ENAS)

Encrypted Network Accelerator Solutions (ENAS) with High-level Security

TCP-TLS 1.3 for Secure 10/25/50 GigE

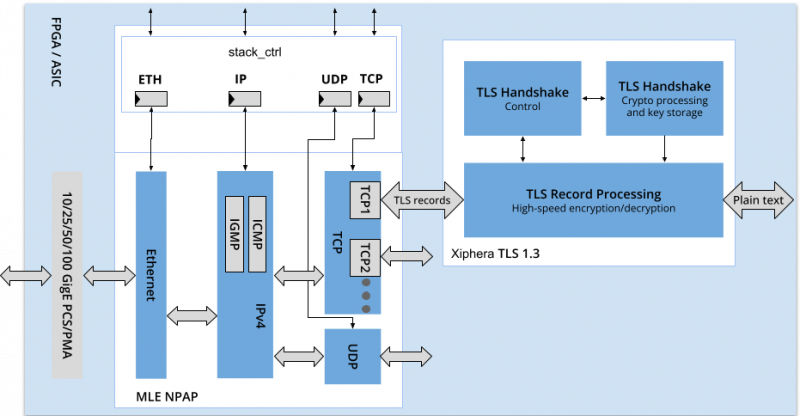

Encrypted Network Accelerator Solutions (ENAS) are joint solutions of MLE’s TCP/IP Network Protocol Accelerator Platform (NPAP) and Xiphera’s TLS 1.3 to ensure secure and reliable connection between devices over LAN and WAN. It implements Transport Layer Security (TLS), a cryptographic protocol that provides end-to-end data security, on top of the Transmission Control Protocol (TCP) layer.

ENAS is designed with hardware-based high-level security and enables high-bandwidth, low-latency communication for FPGA-based systems. The TCP-TLS 1.3 IP core can accelerate the device network up to 10/25/50G Ethernet line rates with data being protected through high-speed, hardware-based encryption and decryption under TLS 1.3. All the cryptographic mathematical operations are performed entirely in the FPGA, and the keys are stored in dedicated internal FPGA memory.

Since the TCP/IP stack and the TLS 1.3 security protocol – including importantly both key exchange and key management – are both executed entirely in hardware, the joint solution has both scalable high-speed performance and minimise attack surface, especially when compared to a software-based approach. The FPGA hereby utilises the hardware Root of Trust, best suited for applications like critical communication in defense, space technology, and energy production and distribution .

Core Benefits

- Resource-optimised IP core available for FPGAs and ASIC designs

- High-speed traffic encryption and decryption

- Secure design – Isolated processing and key management

- All communication layers pre-designed for effective and fast integration

Key Features

- Highly modular TCP/UDP/IP stack with line rate up to 70Gbps in FPGA

- Compact TLS 1.3 implementation

- Hardware-based key management for IEC 62443 SL 3

- Encrypted throughput of 10/25/50 Gbps

- 128-bit bi-directional data paths with streaming interfaces

- Multiple, parallel TCP engines for scalable processing

Secure Communications for Applications Like

- FPGA-based SmartNICs

- In-Network Compute Acceleration (INCA)

- Networked storage, such as iSCSI

- Test & Measurement connectivity

- Automotive backbone connectivity

- System-of-Systems communication

- Mission-critical environments

Resource Utilization Estimation for 10GbE

| AMD/Xilinx Zynq Ultrascale+ | LUT | FFs | RAMB 36 | RAMBI 8 | DSP 48 |

|---|---|---|---|---|---|

| NPAP ( Including MAC, ETH, IPv4, UDP, 3x TCP)* | 33,500 | 35,000 | 71 | 10 | 6 |

| TLS1.3 (Including Crypto Engine, Key storage and handling)* |

43,000 | 28,000 | 25 | 18 | 4 |

| Total | 76,500 | 63,000 | 96 | 28 | 4 |

Pricing

MLE’s Encrypted Network Accelerator Solutions (ENAS) is available as a combination of Intellectual Property (IP) Cores, reference designs, and design integration services:

| Product Name | Deliverables | Example Pricing |

|---|---|---|

| Network Processing Device | Integrated processing device solution, built on top of leading FPGA technology, encapsulating one or more Encrypted Network Accelerators for 10GbE, 25GbE and/or 50GbE. |

Based on NRE and unit volume |

| Intellectual Property (IP) Cores | Single-Project or Multi-Project Use; ASIC or FPGA; Modular and application-specific IP cores, and example design projects; delivered as encrypted netlists or RTL. | Inquire |

| Evaluation Reference Design (ERD) | Available upon request as FPGA design project, with optional customizations (different target device, different transceivers, etc) | free-of-charge |

| Application-specific R&D Services | Advanced network protocol acceleration R&D services with access to acceleration experts from MLE and/or Xiphera. | $1,880.- per engineering day |

Documentation

- Encrypted Network Accelerator Solutions (ENAS) Datasheet by MLE and Xiphera

- TCP-TLS 1.3 for Secure 10/25/50 GigE

- Short session establishment time

- High-speed traffic encryption and decryption

- Hardware-based security, cryptographic operation, and key management

Xiphera Ltd.

Xiphera, Ltd, is a Finnish company designing hardware-based security solutions using standardised cryptographic algorithms. We have strong cryptographic expertise, extensive experience in system design, and deep knowledge on reprogrammable logic, enabling us to protect our customers’ critical information and assets.

Xiphera’s product portfolio consists of secure and efficient cryptographic Intellectual Property (IP) cores, designed directly for Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). Our widely applicable solutions for various end markets offer our customers peace of mind in a dangerous world.