XAUI/RXAUI

AMD/Xilinx Legacy IP Cores for XAUI/RXAUI

The Xilinx XAUI/DXAUI IP Core and the Xilinx RXAUI IP Core used to be part of the Xilinx Vivado tool chain until 2019.1 and was available Xilinx End User License Agreement. As of May 2020, Xilinx handed over support and distribution of the XAUI/RXAUI IP Cores to MLE. MLE has been supporting customer projects with these IP Cores and will continue to provide to Xilinx users long term support.

We are able to include the Questa/Mentor public key into our encrypted IP-Cores, which allows us to integrate the IPs via Vivado or simulate the IPs in Questa (requires IEEE1735 V2 encryption). Depending on customer needs, we generate encrypted netlists or encrypted source code.

XAUI IP Cores

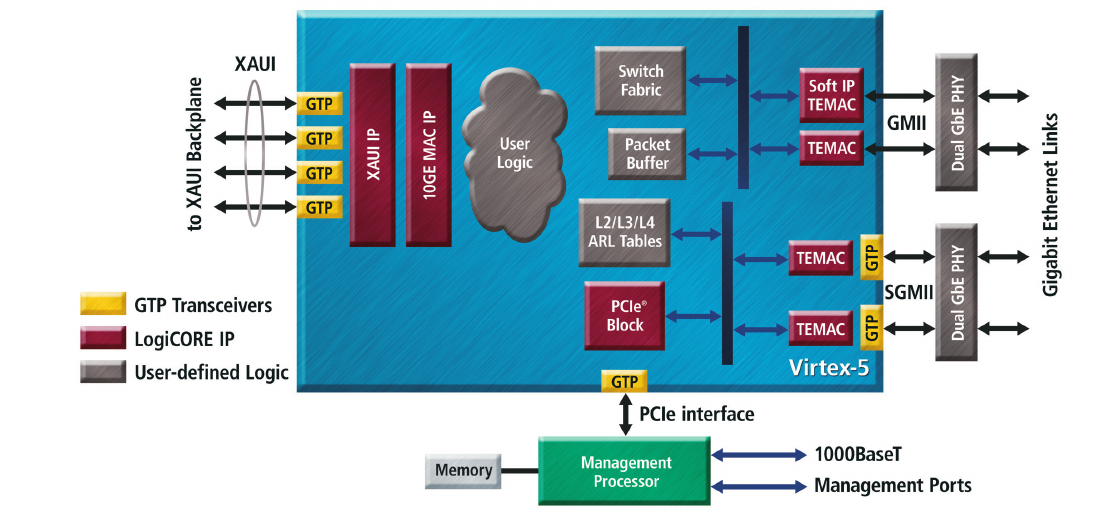

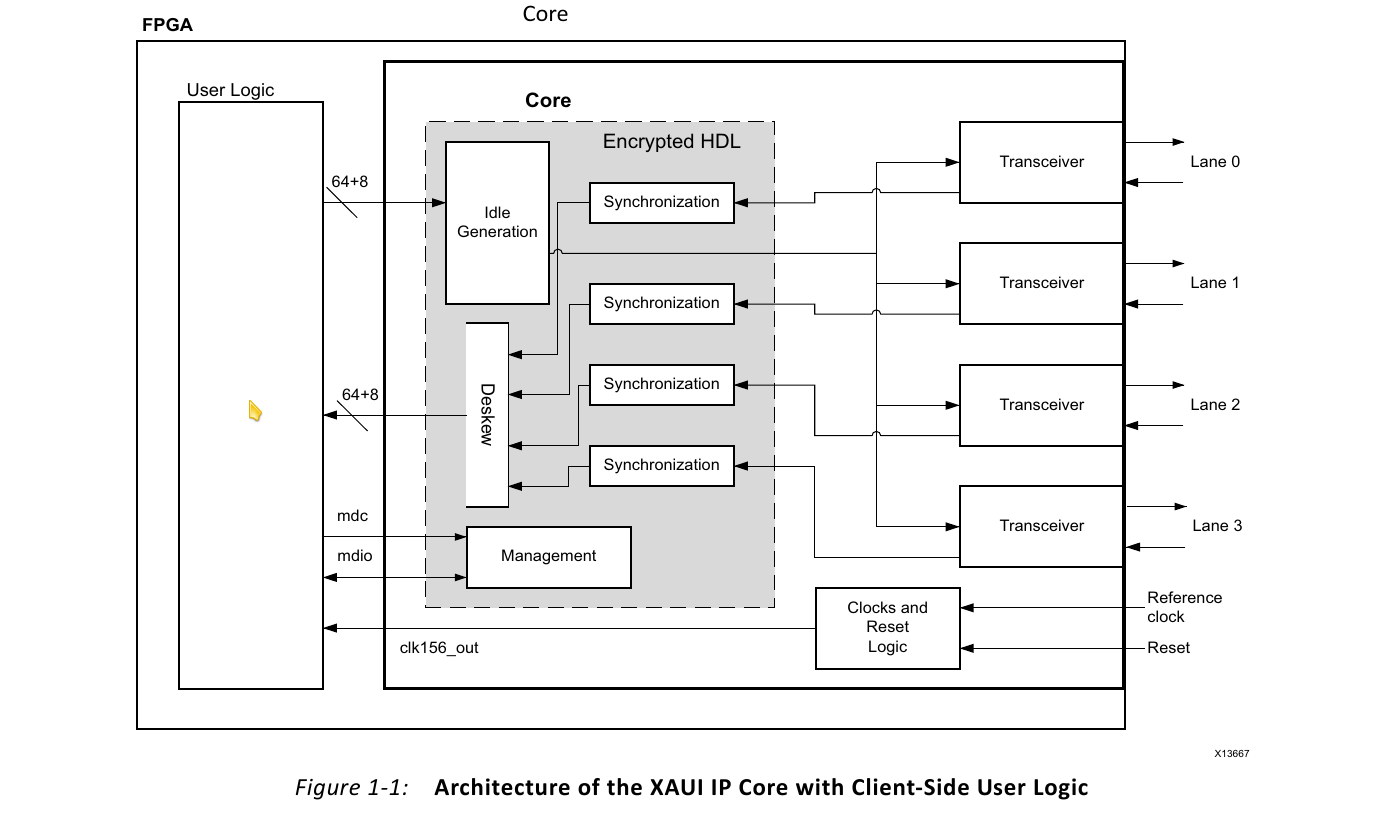

The Xilinx XAUI (eXtended Attachment Unit Interface) IP Core is a high-performance, low-pin count 10-Gb/s interface intended to allow physical separation between the data link layer and physical layer devices in a 10-Gigabit Ethernet system.

The XAUI core implements a single-speed full-duplex 10-Gb/s Ethernet eXtended Attachment Unit Interface (XAUI) solution for the UltraScaleTM architecture (GTHE3 transceivers), Zynq®-7000 All Programmable SoC, and 7-series devices.

RXAUI IP Cores

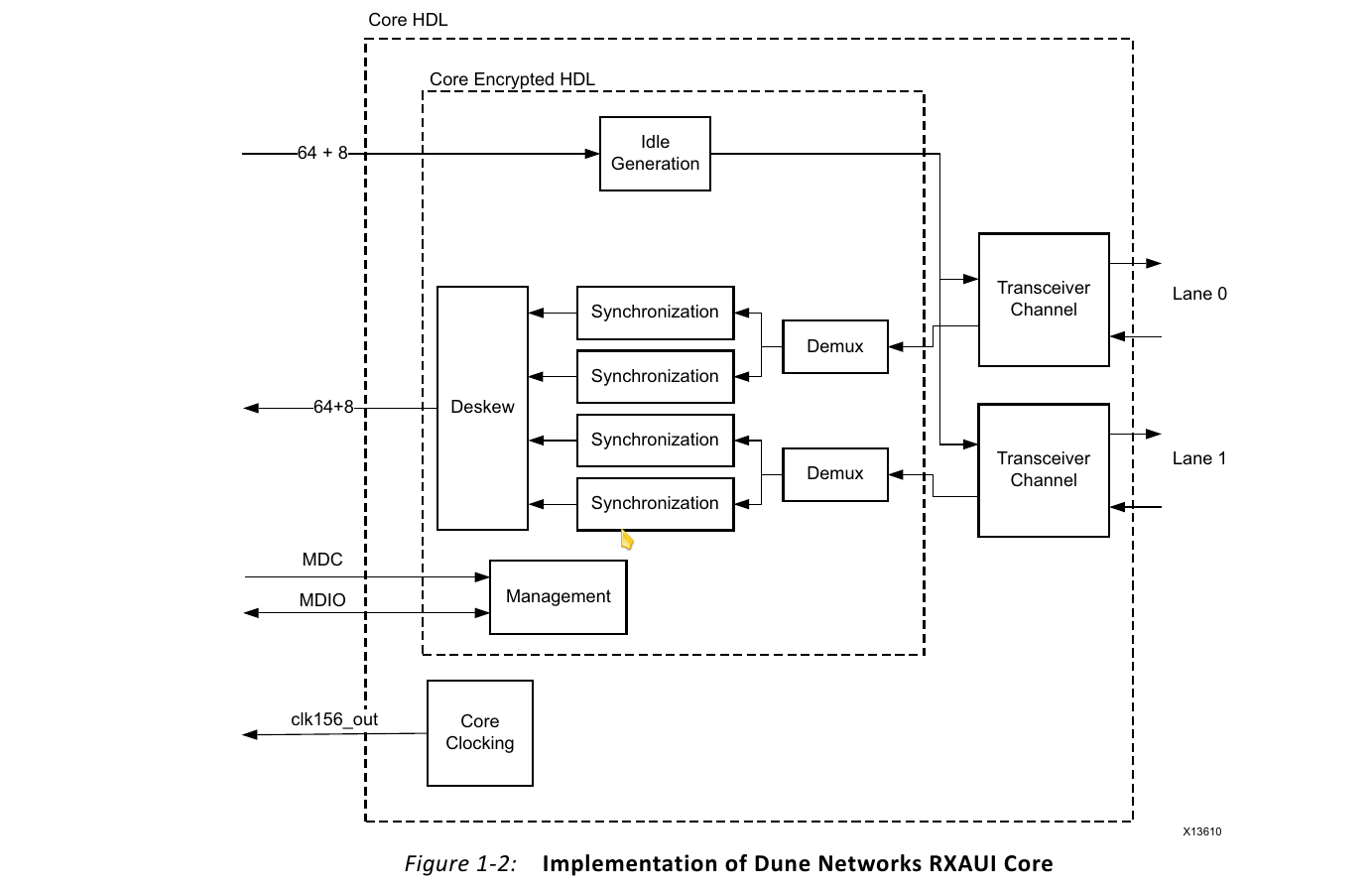

The Xilinx LogiCORE IP RXAUI core is a high-performance, low pin count 10 Gb/s interface intended to allow physical separation between the data-link layer and physical layer devices in a 10 Gb/s Ethernet system.

The RXAUI core implements a single-speed full-duplex 10 Gb/s Ethernet Reduced Pin eXtended Attachment Unit Interface (RXAUI) solution for Xilinx® 7 series FPGAs and UltraScale architecture (GTHE3 transceivers) that comply with Dune Networks specifications. The 7 series FPGA and UltraScale architecture in combination with the RXAUI core, enable the design of RXAUI-based interconnects whether they are chip-to-chip, over backplanes, or connected to 10 Gb/s optical modules.

Pricing

The XAUI/RXAUI IP Cores are available as Intellectual Property (IP) Cores and design integration services:

| Product Name | Deliverables | Pricing |

|---|---|---|

|

XAUI IP Core |

Single-Project-Use; delivered as encrypted netlist. |

$14,500.- |

|

RXAUI IP Core |

Single-Project-Use; delivered as encrypted netlist. |

$14,500.- |

| XAUI IP Core | Multi-Project-Use; delivered as encrypted netlist. | $21,800.- |

| RXAUI IP Core | Multi-Project-Use; delivered as encrypted netlist. | $21,800.- |

| XAUI and RXAUI IP Core Bundle | Single-Project-Use; delivered as encrypted netlist. | $21,800.- |

| XAUI and RXAUI IP Core Bundle | Multi-Project-Use; delivered as encrypted netlist. | $28,800.- |

|

Application-specific R&D Services |

Network protocol expert design services. |

$1,880.- per engineering day (or fixed price project fee) |

Documentation

- RXAUI v4.3 LogiCORE IP Product Guide PG083 (Oct 5, 2016)

- XAUI v12.1 LogiCORE IP Product Guide PG053 (Nov 19, 2014)