Partners Trenz Electronic and MLE co-exhibit at Embedded World 2024 and present solutions for you to “shift-left” your FPGA design projects. Use our FPGA Full System Stacks which comprise off-the-shelf FPGA System-on-Modules (SoM) from Trenz Electronic plus FPGA subsystems and IP cores from MLE!

Trenz & MLE Help "Shift-Left" Your FPGA Design

FPGA Full System Stacks Combine Trenz SoMs and MLE IP-Cores

Trenz Electronic offers a variety of leading edge, high-quality FPGA System-on-Modules (SoMs) built with FPGAs of AMD/Xilinx, Altera and Microchip.

MLE’s FPGA Full System Stacks have a particular focus on high-speed connectivity using PCI Express, MIPI CSI-2, GMSL, Multi-Gigabit Ethernet.

The combination of Trenz FPGA SoMs and MLE FPGA Full System Stacks target applications which require reliable, low-latency, high-throughput network transports, high-speed data acquisition, augmented stereo computer vision, high-speed data record & replay. All those are driven by AI algorithms processing massive data from high-resolution cameras, Radar and Lidar sensors.

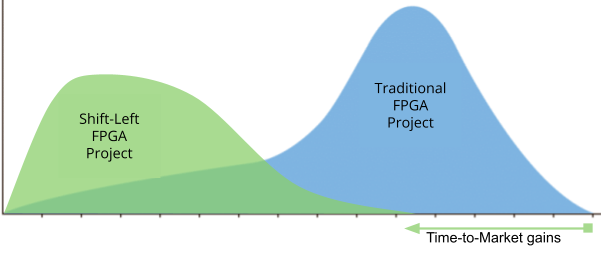

Shorten Time-to-Market

By using the off-the-shelf FPGA-based System-on-Modules and pre-validated, parameterizable FPGA IP-Cores and subsystems, MLE and Trenz can develop the FPGA software and design PCB concurrently while reducing risks and optimizing costs.

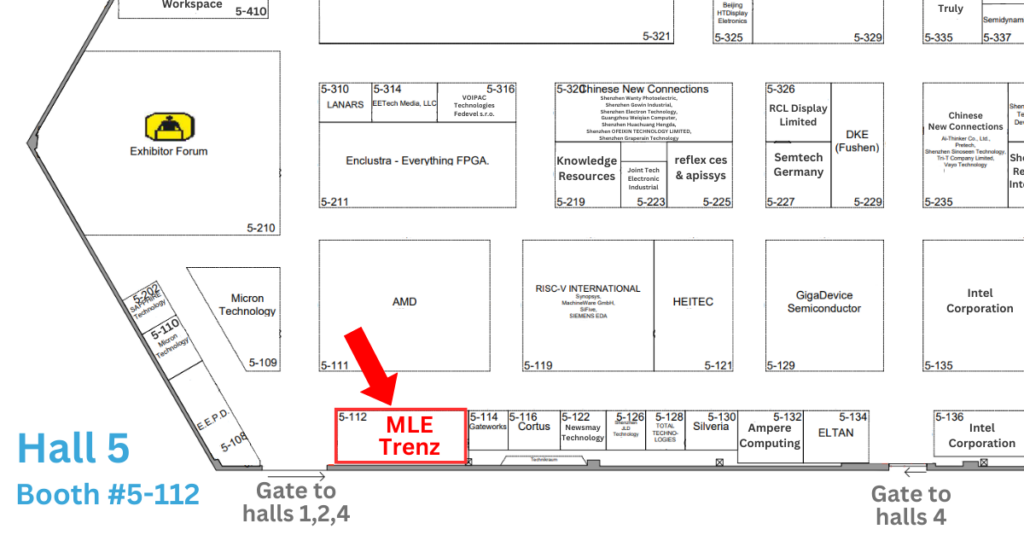

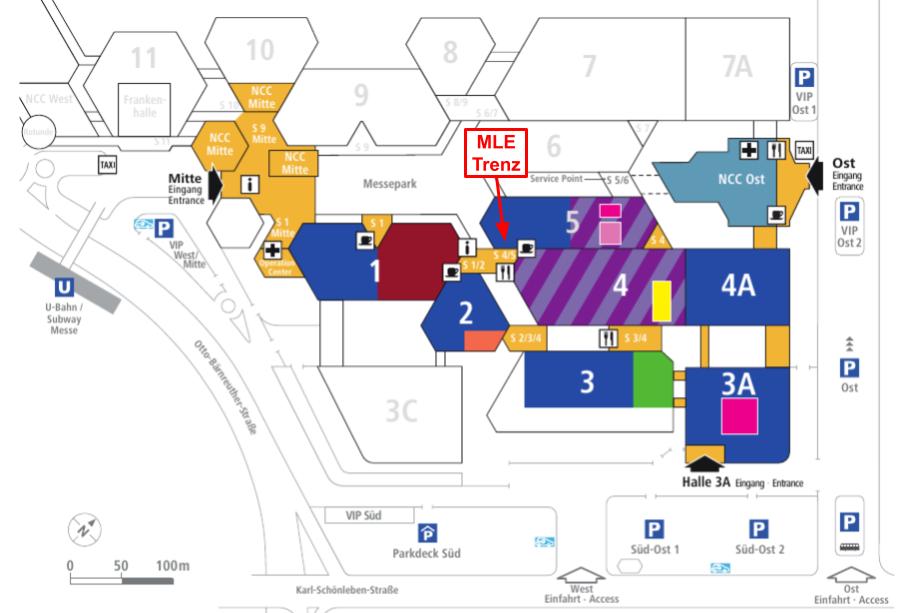

Visit us at Embedded World 2024 to experience the featured solutions!

Hall 5 #5-112

FPGA Full System Stacks Live Demo

Built on Top of Trenz Latest SoMs

FPGA Full System Stacks Examples

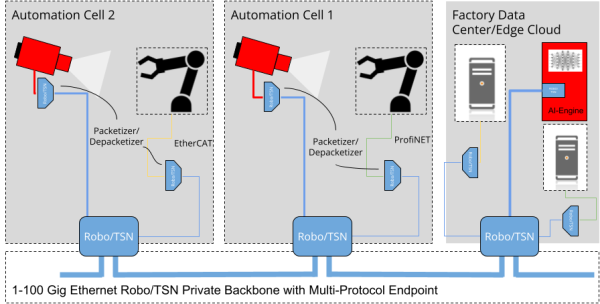

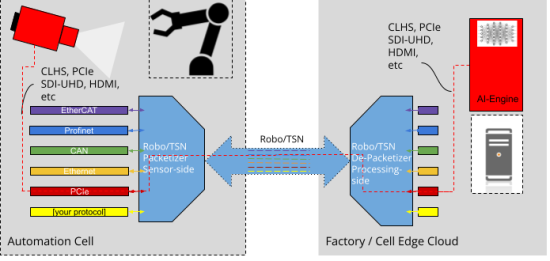

Robo/TSN

MLE’s Robo/TSN full system stacks allows it to tunnel modern multi-Gig sensor data (GigEVision, PCIe, MIPI CSI-2, GMSL) as well as industrial protocols like Ethercat or Profinet.

Features:

- Tunnel several protocols like PCIe, Ethercat, Profinet, CAN…

- Scalable from 1 to 100 Gbps

- Precision time synchronization with IEEE TSN or IEEE 1588 v2

- Deterministic transport with Ultra Low Latency (RTT < 600 ns)

- Reliable transports via TCP/IP and/or Quad-RP/IP

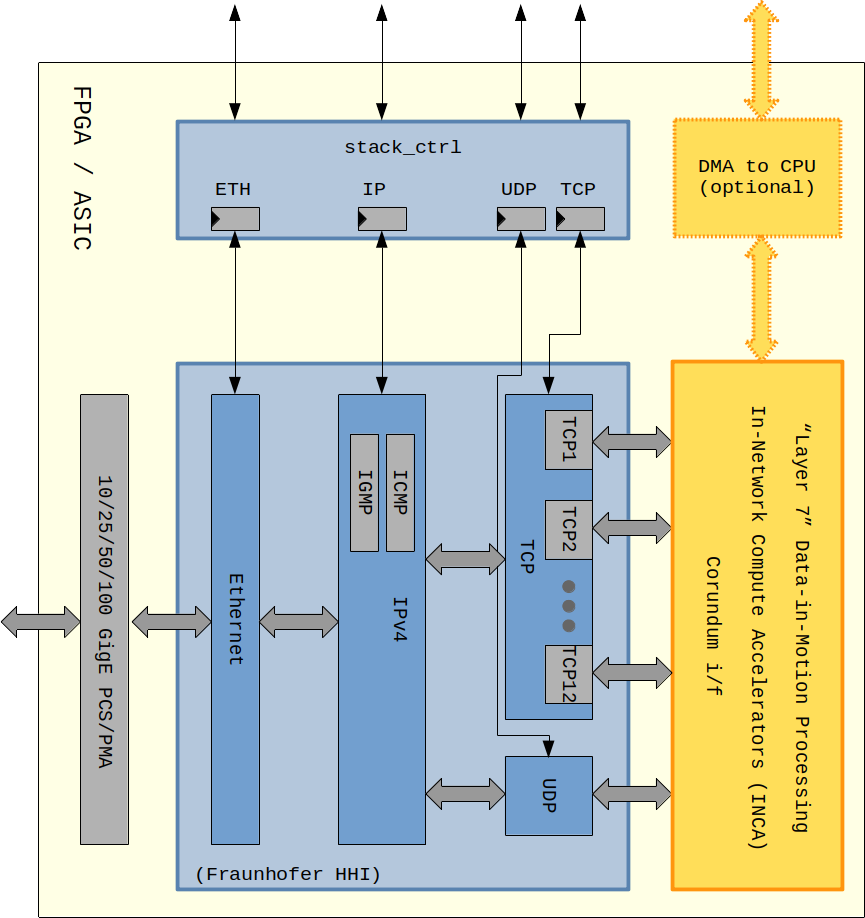

Network Protocol Acceleration Platform (NPAP)

MLE’s network accelrators “TCP/IP & UDP Network Protocol Accelerator Platform (NPAP) enables high-bandwidth, low-latency communication solutions for FPGA- and ASIC-based systems for 1G / 2.5G / 5G / 10G / 25G / 40G / 50G / 100G Ethernet links.

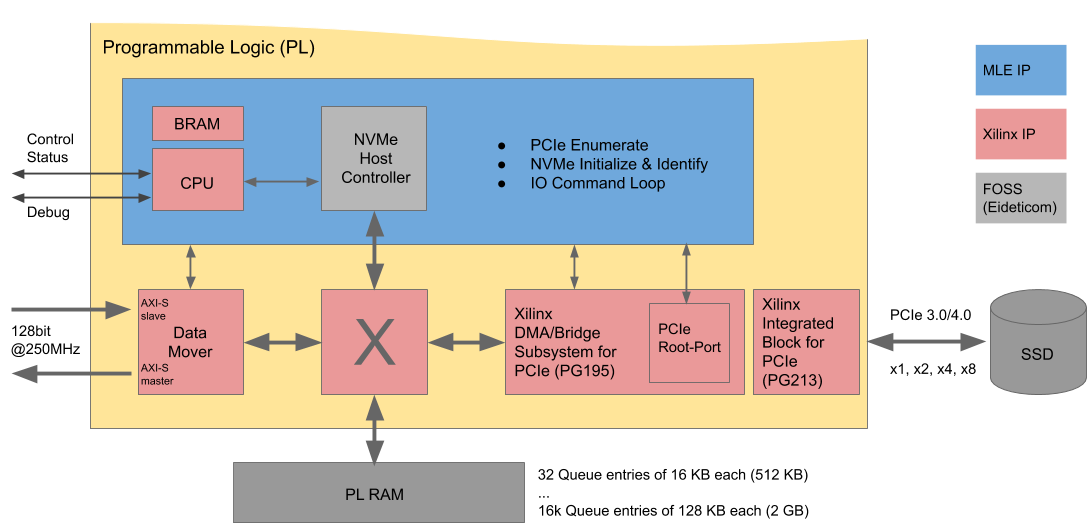

NVMe Streamer

MLE’s NVMe Streamer, the Full Accelerator NVMe host subsystem, enables high read/write bandwidth and performance scalability for high speed data recording and re-play without any CPUs involved.

Embedded World Conference 2024

Join EW24 Conference for MLE's latest FPGA technology regarding embedded networking acceleration for high-speed data streaming.

Session 2.5: starts 1:45pm CEST

April 9th, 2024 (Tue)

Speaker: Endric Schubert, CTO, MLE

Session 8.2: starts at 1:45pm CEST

April 10th, 2024 (Wed)

Speaker: Andreas Schuler, Director Applications, MLE

Session 1.9: starts at 2:30pm CEST

April 11th, 2024 (Thu)

Speaker: Ulrich Langenbach, Director Engineering, MLE

Visit us at booth #5-112 and talk with our FPGA experts to learn about how to shift-left your FPGA design projects with FPGA Full System Stacks!

Yi-Ying Li (Sandy)

Director Technology Solutions

yiying.li@missinglinkelectronics.com