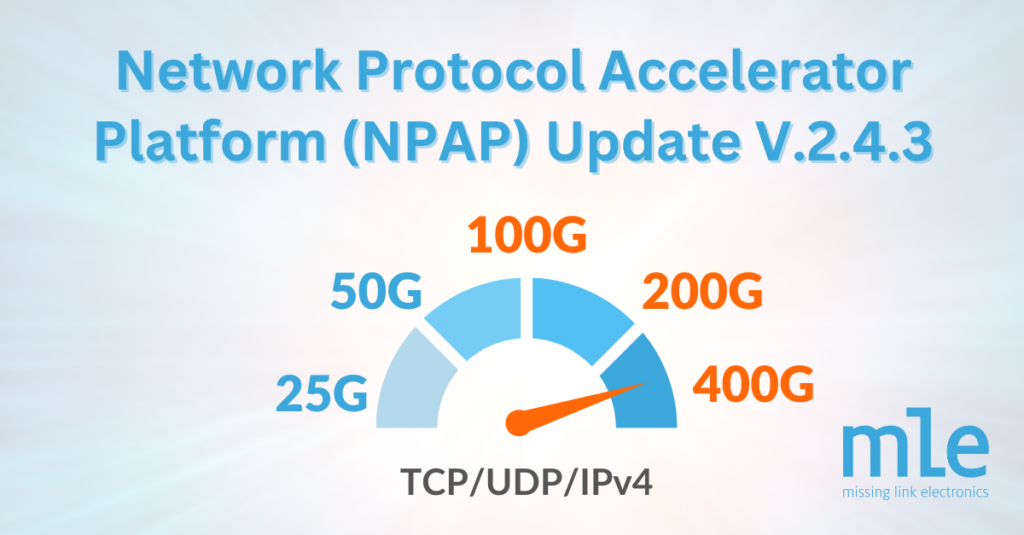

MLE has released an update, Version 2.4.3., of its Network Protocol Acceleration Platform (NPAP).

MLE’s Network Protocol Accelerator Platform (NPAP) runs the entire TCP/UDP/IPv4 protocol stack in a digital circuit, i.e. FPGA or ASIC. This means NPAP must meet some challenging combinations of Your requirements:

- First (and most important of all), NPAP must be compatible and fully interoperable with the many TCP/UDP/IP software stacks in use today

- Second, users expect outstanding performance: High throughput (close to line rate) and low latency (in form of short Round-Trip Times)

- Resource efficiency comes next: This means avoiding “FPGA Bloat” as well as options to tune Rx and Tx buffer sizes

- Then, users want us to support leading FPGA vendors and device families with their many different high-speed transceivers and Ethernet subsystems

- And last, a clean and affordable license model that makes sense even for low unit volume applications such as in Test & Measurement

Over the years, MLE’s engineering team has invested significantly in NPAP’s test automation. CI (continuous integration) tools such as Gitlab integrating Pytest for simulation and hardware test cases have enabled us to run the TCP/IP stack on many different FPGA boards, to interact with different software stacks such as the many versions in the open source Linux kernel, Microsoft® Windows with its many flavors, kernel bypass implementations such as AMD SolarFlare® Onload or Nvidia® Mellanox Messaging Accelerator (VMA), for example.

One key feature to be FPGA resource efficient is the underlying 128 bit wide dataflow architecture, as this balances throughput, FPGA clock speeds and avoids “FPGA Bloat”. Other features include options for QoS (Quality-of-Service) to prioritize some TCP streams over others and means for asymmetric buffer management.

We have put special focus on cornercases which impact performance, such as Bit Errors on the wire which cause TCP Re-Transmissions which, again, cause the net throughput to drop.

An (optional) Bit Error Insertion module facilitates Your integration and testing for “not so standard” Ethernet links: Over the years we have seen systems using very low power PHYs, multiple slip-rings, “special” connectors, and such, and wanted everything just to work as much as our customers!

Thanks to the great enablement from our FPGA partners, we have always been able to start migration and testing once new FPGA hardware enters the market.

Today, MLE NPAP runs on (almost) all AMD devices starting from 7-series up to Versal (with clear plans for Versal Gen 2), and on many of those AMD Alveo cards, too.

After great collaboration with engineers at Altera and Arrow, we are about to release MLE NPAP for the new Altera Agilex 5 FPGAs as we finish testing on the Arrow AXE5-Eagle Development Platform.

MLE NPAP is regularly tested for Microchip PolarFire because this is important to our customers from the low-power, cost-optimized world of FPGA based cameras and computer vision.

And, driven by novel use cases in automotive and factory automation, we are looking forward to releasing MLE NPAP for the Avant G/X series FPGAs from Lattice Semiconductor.

If you have been a licensee of MLE NPAP who is interested in upgrading to the latest latest Version 2.4.3, or if your new project can benefit from reliable TCP/UDP/IP connectivity, please contact your MLE sales representative.