Trenz Electronic GmbH (Trenz), Hüllhorst, Germany, and Missing Link Electronics, Inc. (MLE), San Jose, CA, both Premier Members of the AMD Adaptive Computing Partner Program, have entered a strategic partnership to provide FPGA-based Turnkey Solutions and Full System Stacks, extending their European collaboration to Canada and the United States.

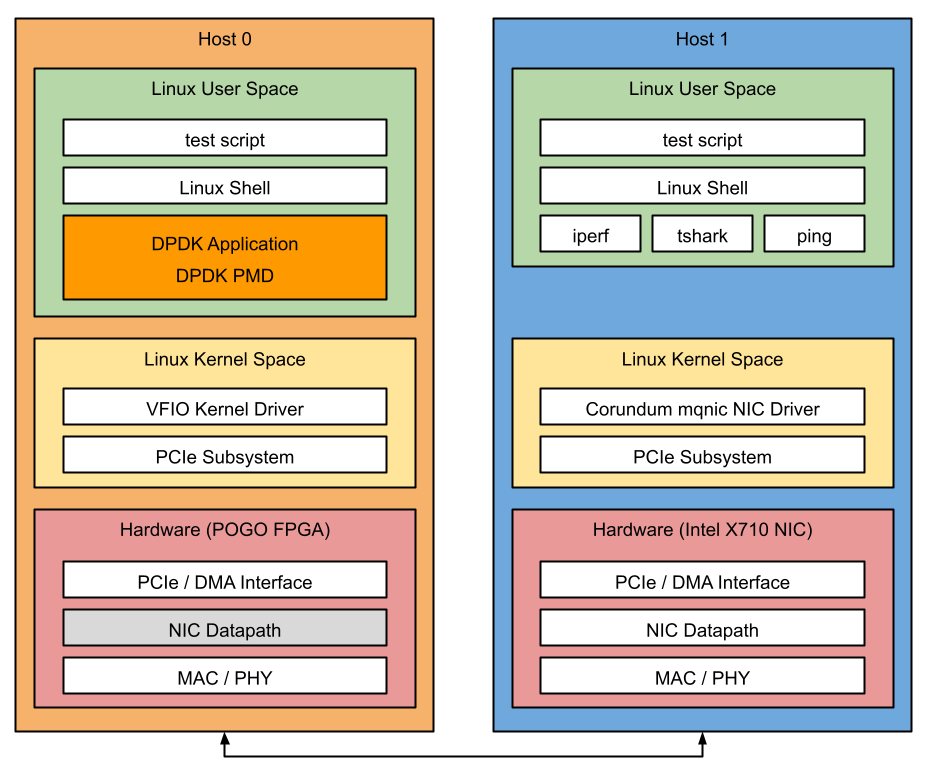

The market for Field-Programmable Gate Arrays (FPGA) continues to grow significantly owing to its increasing performance, flexibility, cost and energy benefits in various end-use industries: Automotive, Aerospace/Defence, Industrial/Scientific/Medical, Compute, Wired and Wireless Telecommunication. However, the difficulty in programming FPGAs, in particular those System-on-Chip (SoC) FPGA with embedded CPUs, has long been considered a disadvantage that prevents FPGA from becoming a general computation solution. Integrated and pre-validated building blocks such as Trenz’ System-on-Modules (SoM) FPGA hardware and MLE’s Compute, Video, Storage and Networking FPGA software subsystems significantly increase the productivity of end-users of FPGAs while shortening time-to-market for new product initiatives.

The aim of this strategic partnership is to de-risk and to cost-down High-Performance Compute and Embedded Systems by delivering complete FPGA Turnkey Solutions and Full System Stacks to end users in volume.

Trenz and MLE have established close engineering collaboration and a track record of shipping integrated FPGA solutions based on Trenz SoM running MLE’s System Software Stacks with Compute, Video, Storage and/or Network Acceleration. Given MLE’s presence in the heart of Silicon Valley, this new level of partnership gives customers in the USA and Canada easy access to FPGA-based cards, boards, SoMs from Trenz along with IP Cores, design services and engineering support from MLE experts.

A 40 GigE SD-WAN Access Point and Customer Premise Equipment – which is now shipping to a green-field telco customer in Canada – is a typical example of this close partnership: To de-risk the project, MLE started with the AMD Zynq UltraScale+ MPSoC on the Trenz SoM TE0808 within a Trenz Starter Kit and could deliver a working Proof-of-Concept within weeks. Based on this success, MLE modified the Trenz carrierboard TEBF0808 to meet the customer’s connectivity requirements. Again, manufactured by Trenz Electronic Manufacturing Services (EMS), the first product shipped within less than a year. For volume ramp-up Trenz and MLE are planning a so-called chip-down solution (unifying the SoM with the baseboard to a single PCB) which maintains key system/software compatibility but shrinks the hardware Bill-of-Materials (BoM) costs.

Since 1992 Trenz Electronic has operated as a provider of development and production services for the electronics industry. Services include design-in support as well as turnkey designs which typically covers all steps from product specification, hard- and software design up to prototyping and production. Trenz specializes in the design of high-speed data acquisition, high-accuracy measurement and embedded digital signal processing systems based on FPGA and CPU architectures. Trenz development service is supplemented by FPGA-and MCU-based development boards and tools.

About MLE

Head-quartered in Silicon Valley with engineering offices in Berlin and Neu-Ulm, Germany, Missing Link Electronics (MLE) has successfully delivered solutions for Wired and Wireless Telecommunications, Datacenter storage, network protocol and algorithm acceleration in the cloud, Autonomous Driving and ADAS and Image processing and sensor fusion with camera, Radar, Lidar sensors etc.