Algoblu announced today its Network Element Virtualization (NEV) platform that virtualizes and orchestrates underlying network resources to help carriers offer more application-oriented customized services to both commercial and residential customers. Thanks to the new FPGA-based technology, the cost per bit decreases by more than four times and operation efficiency increases three times.

Algoblu announced today its Network Element Virtualization (NEV) platform that virtualizes and orchestrates underlying network resources to help carriers offer more application-oriented customized services to both commercial and residential customers. Thanks to the new FPGA-based technology, the cost per bit decreases by more than four times and operation efficiency increases three times.

“We are pleased to collaborate with Algoblu to develop a Network Element Virtualization chip built on leading-edge FPGA technology. The chip is key to Algoblu’s NEV architecture with an FPGA-based SMartNIC, all developed in an elegant way,” says Dr. Endric Schubert, CTO at Missing Link Electronics.

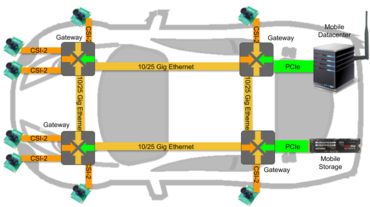

![]() MLE will present "Zone-Based Architectures with Auto/TSN on Zynq UltraScale+ MPSoC" at the Xilinx Adapt EMEA: Automotive. This is organized as a Virtual Technical Event in the mornings of May 18-19, 2021.

MLE will present "Zone-Based Architectures with Auto/TSN on Zynq UltraScale+ MPSoC" at the Xilinx Adapt EMEA: Automotive. This is organized as a Virtual Technical Event in the mornings of May 18-19, 2021.

MLE participated as sponsor and as a presenter of “Zone-Based Automotive Backbones Tunneling PCIe” at the

MLE participated as sponsor and as a presenter of “Zone-Based Automotive Backbones Tunneling PCIe” at the