Auto/TSN

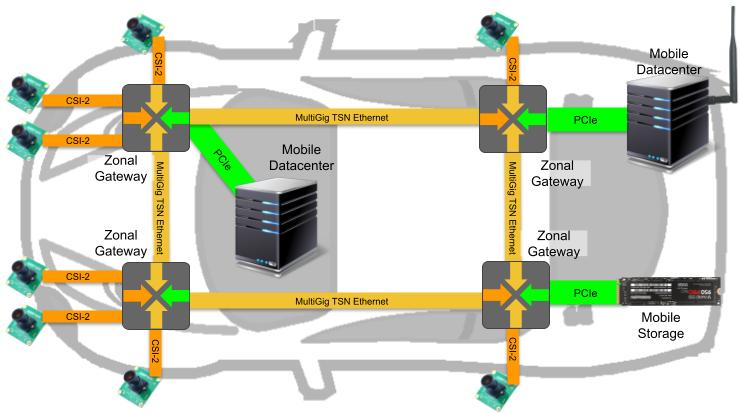

In-Vehicle Network - Auto/TSN

Auto/TSN stands for automotive data over Time-Sensitive Networks which is an in-vehicle network infrastructure based on open standards such as IEEE Ethernet. Auto/TSN is the results of a collaborative effort between MLE and MLE partners from Fraunhofer.

Fundamentally, Auto/TSN virtualizes the in-vehicle network infrastructure: Key objective is to reduce costs, increase scalability and enable upgradability for next-generation automotive architectures including electric and/or autonomous vehicles.

By tunneling sensor data along with PCIe and NVMe over Real-Time Multi-Gigabit Automotive Ethernet Auto/TSN simplifies the wire harness and enables more centralized architectures with higher levels of hardware / software integration. By offering PCIe as a common interface (for sensor-to-CPU and CPU-to-CPU connectivity) Auto/TSN different semiconductor SoCs become interchangeable. This significantly reduces semiconductor dependencies and infrastructure costs at the same time.

Auto/TSN is highly scalable and supports line-rates up to 50 Gbps in FPGA and 100 Gbps in ASIC. It is agnostic to the physical layer and can, for example, run over the new IEEE 802.3cz-2023 optical fiber standard for automotive.

Based on IPv4, the space for addressing nodes is 32 bits wide. The small hardware footprint allows zonal gateways with many ports. Auto/TSN is “software-defined” and builds from open standards such as IEEE 802.1Q TSN, IEEE 802.3 Ethernet, IETF TCP/IP, MIPI CSI-2, PCIe 4.0 and NVMe 1.4 and open-source Linux which eases hardware / software / system upgradability.

Features & Benefits of In-Vehicle Network Auto/TSN

Auto/TSN is a network infrastructure with a system/software focus which reduces the complexity of connecting sensors and centralized computers because it follows de-facto standards of open source network APIs such as RDMA, Linux netdev or SOME/IP.

Benefits include:

- Significant cost-down for in-vehicle networking and wire harnesses

- Digital circuit implementation for zero CPU load

- Deterministic and very low transport latencies, typ. within 5 micro-seconds

- Low footprint enables ASIC or FPGA implementation

The current implementation of TSN supports time-synchronization (IEEE 802.1AS) with 20 nanosecond precision, traffic shaping (IEEE 802.1Qav, 802.1Qbv), frame replication (IEEE 802.1CB) and stream prioritization (IEEE 802.1Qat) for high reliability, low-cost redundancy for functional safety and real-time behavior. Because for PCIe “best effort” is not sufficient, Auto/TSN implements a reliable transport on top of TSN which is compliant to IETF TCP/IP.

For in-vehicle network security Auto/TSN can be complemented with state-of-the-art IEEE 802.1AE MAC Security Entities (MACsec) and/or IETF RFC 6071 Internet Protocol Security (IPsec) and/or IETF RFC8446 Transport Layer Security (TLS).

Various Connectivity Schemes are supported:

- Single CPU (PCIe Root-Port) to multiple devices (PCIe Endpoints)

- Single CPU to multiple SSDs via NVM Express (NVMe)

- Multiple CPUIs to multiple NVMe SSDs (via NVMe proxy)

- Multiple CPUs to multiple CPUs via Inter-System Bridge (a.k.a. PCIe NTB)

- Asymmetric sensor connectivity, e.g. MIPI CSI-2 to PCIe

- IEEE 1722 style video transport

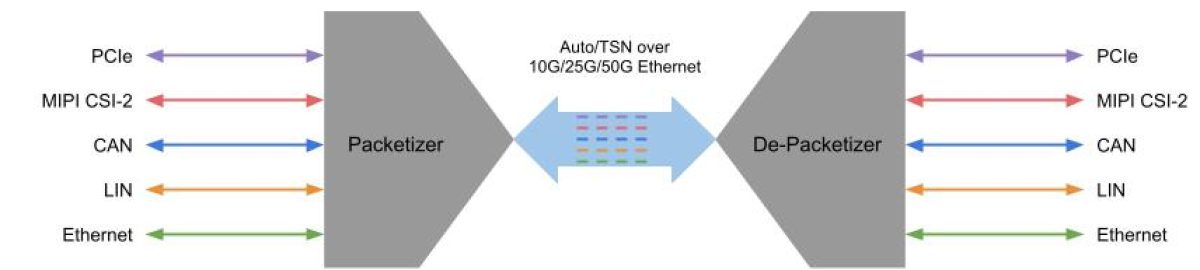

Data-in-motion processing runs on dedicated on-chip full accelerators and frees up the CPUs from protocol handling. Our patented and patent-pending Heterogeneous Packet-Based Transport mechanism packetizes and de-packetizes PCIe, MIPI CSI-2 and other packet-based protocols and features low protocol overhead for high bandwidth and low and deterministic micro-second transport latency.

PCIe Over Auto/TSN

Auto/TSN implements a PCIe switch compliant with PCI-SIG Base Specification 3.0 (or newer) and NVM Express Specification 1.2 (or newer).

PCIe Inter-System-Bridge for Auto/TSN

Integrated PCIe Inter-System Bridges (a.k.a Non Transparent Bridges / NTB) enable CPU-to-CPU connectivity. The PCIe Inter-System Bridges use a least-cost write-only protocol to deliver very high read/write performance. This allows direct connectivity between sensors and multiple CPUs, GPUs, FPGA, SoCs, peripherals and next-generation storage within the entire vehicle.

MIPI CSI-2 Over Auto/TSN

Image sensors can connect via standard MIPI D-PHY and MIPI CSI-2, or else. Multicast functionality transports data from each image sensor to one, or more, central compute units under real-time conditions. Hence, Auto/TSN allows symmetric (e.g. PCIe-to-PCIe) and asymmetric (e.g. MIPI CSI-2-to-PCIe) communication schemes.

IEEE 1722 Video Transport Over Auto/TSN

Complementing the MIPI CSI-2 over Auto/TSN transport, MLE has also implemented a solution that follows the Raw Video PDU Format from IEEE 1722.Similarly, this IEEE 1722 Raw PDU Transport supports point-to-point connectivity or multicast where one sensor's image data can be sent to multiple CPUs simultaneously.

Availability

Auto/TSN is available as a licensable integrated subsystem stack comprising digital circuit implementations and device driver software. This business model gives OEMs and Tier1s full control over how to integrate, either as a dedicated semiconductor component, or as modular function blocks inside a custom System-on-Chip with additional customer-specified functionality.

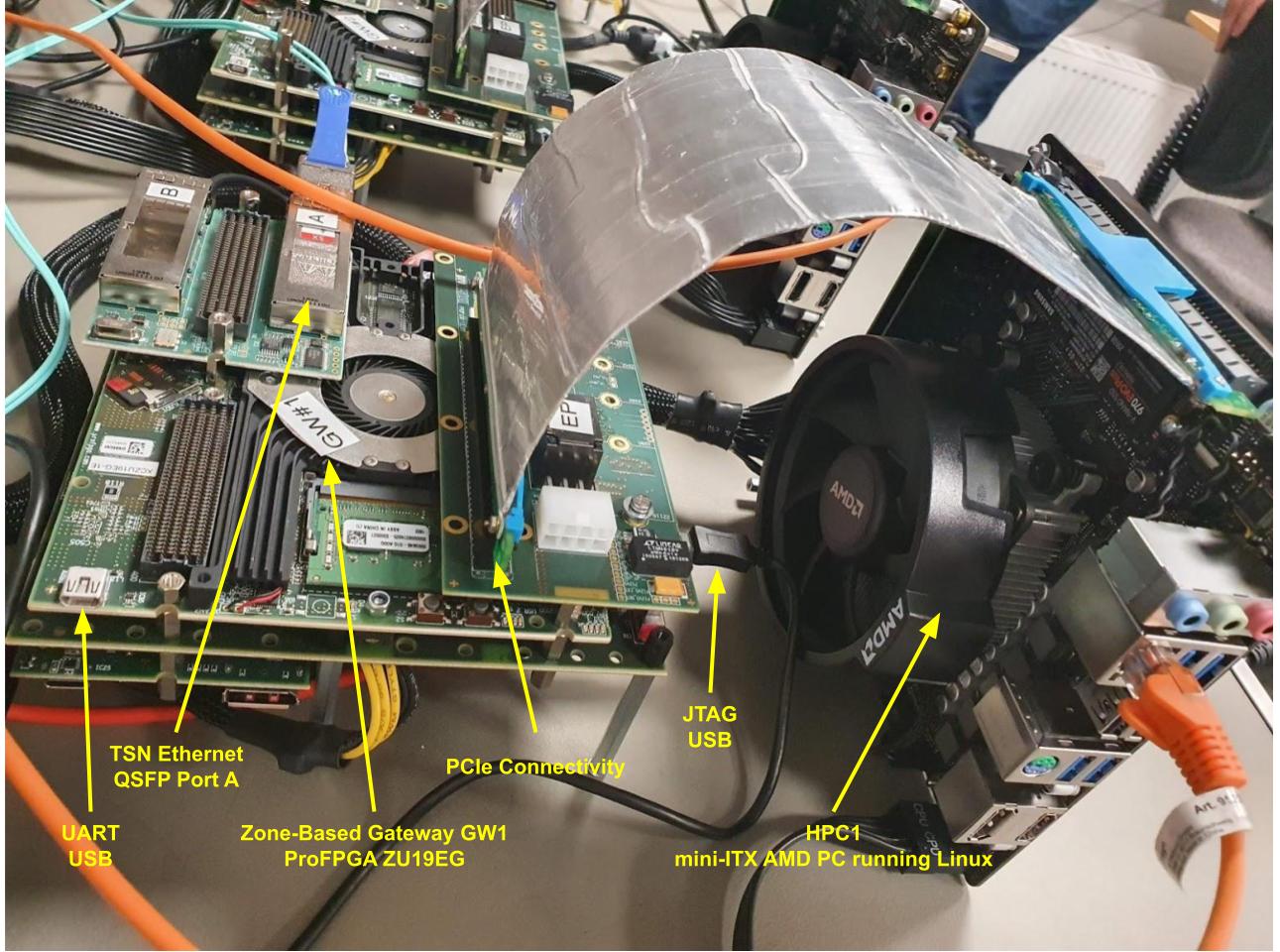

MLE has been working with key semiconductor partners to deliver FPGA and ASIC based implementations of Auto/TSN ready for design and for production. Our early access program supports OEMs and Tier1s to perform in-house benchmarking and validation of Auto/TSN.

Current implementations support gateway nodes with PCIe 3.0 and NVMe 1.2 with up to 4 lanes and with 5 or 8 GT/s, MIPI D-PHY 2.0 with up to 4 lanes and 2 Gbps and MIPI CSI-2 2.0 and up to 8 1G/10G Ethernet ports over copper or over fiber. “Lab Cars” based on professional 3rd party ASIC hardware emulators are available upon request.

Documentation

- Zonal/SDV Architecture Exploration: From Whiteboard to Vehicle Demo in 9 Months (presented at AMD Technology Day 2025 at Volvo)

- Architecture and Performance of Integrated High-speed and Versatile Embedded Networking (presented at Embedded World 2024)

- Zone-Based Automotive Backbones Tunneling PCIe (presented at PCI-SIG Developers Conference 2021)

- PCIe-over-TCP-over-TSN-over-10/25 GigE (presented at the FPGA-for-ADAS Workshop 2020)

- Sensor Fusion and Data-in-Motion Processing for Autonomous Vehicles (presented at PCI-SIG Developers Conference 2019)

- PCIe Range Extension via Robust, Long Reach Protocol Tunnels (presented at PCI-SIG Developers Conference 2018)

- MLE Auto/RPS and Auto/TSN For In-Vehicle Networking Have Been Featured By The BMFTR MANNHEIM CeCaS Project For Central Car Server

- Zonal/SDV Architecture Exploration: From Whiteboard to Vehicle Demo in 9 Months

- MLE Joins Central Car Server Supercomputing Research for Automotive, Funded by German BMBF (CeCas)

- MLE’s Auto/TSN for Digital RADAR Networks Receives BMBF Funding (VERANO)

- Berlin 6G Conference 2024 for Integrated Communication and Sensing (ICAS)

Fraunhofer Heinrich-Hertz Institute

Founded in 1949, the German Fraunhofer-Gesellschaft undertakes applied research of direct utility to private and public enterprise and of wide benefit to society. With a workforce of over 23,000, the Fraunhofer-Gesellschaft is Europe’s biggest organization for applied research, and currently operates a total of 67 institutes and research units. The organization’s core task is to carry out research of practical utility in close cooperation with its customers from industry and the public sector.

Fraunhofer HHI was founded in 1928 as “Heinrich-Hertz-Institut für Schwingungs- forschung“ and joined in 2003 the Fraunhofer-Gesellschaft as the “Fraunhofer Institute for Telecommunications, Heinrich-Hertz-Institut„. Today it is the leading research institute for networking and telecommunications technology, “Driving the Gigabit Society” .

Fraunhofer Institute for Photonic Microsystems

Fraunhofer IPMS is a worldwide leader in research and development services for electronic and photonic microsystems in the fields of Smart Industrial Solutions, Medical & Health applications and Improved Quality of Life. Innovative products can be found in all large markets – such as ICT, consumer products, automobile technology, semiconductor technology, measurement and medical technology – products which are based upon various technology developed at Fraunhofer IPMS.