SATA Storage Extension for ZYNQ 7000™

Pre-validated ZYNQ SATA Solutions

Since 2010, MLE has been providing SATA connectivity solutions for FPGAs. In 2014, as a result of close collaboration with Xilinx and Asics World Services, a new concept was introduced: To deliver a complete reference design with pre-integrated IP cores plus drivers and application software to reduce NRE costs and risks, and to shrink time-to-market for embedded applications.

This, eventually, became the preferred option to connect SATA Harddisk Drives (HDD) and Solid-State Drives (SSD) to the Xilinx Zynq-7000 All Programmable SoC.

MLE releases this SATA technology to support Xilinx Vivado version 2016.4, Xilinx PetaLinux version 2016.4 with a new Linux kernel 4.6 device API, plus streamlined product offerings to reflect the growing needs of embedded applications.

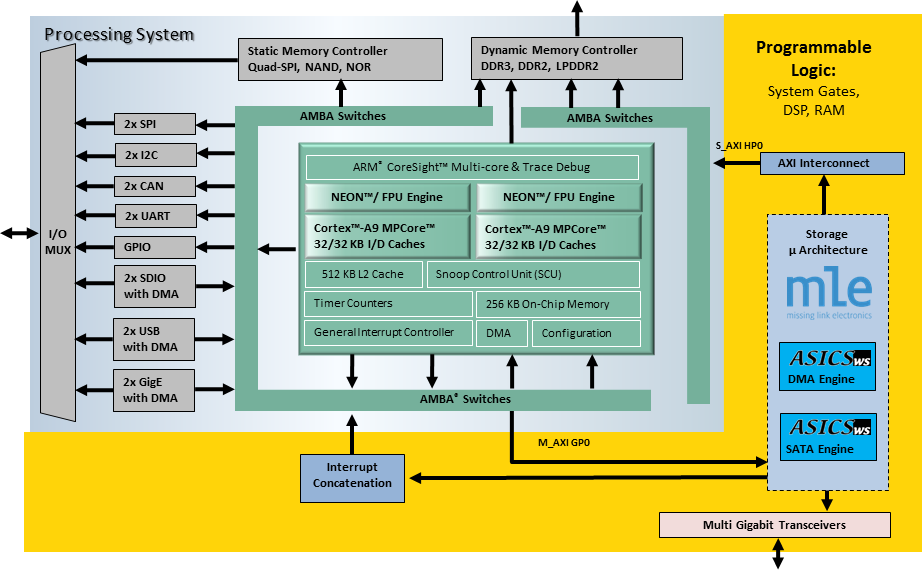

MLE’s mature Zynq SATA Storage Extension (Zynq SSE) has been integrated into many successful customer projects. Zynq SSE responds to the embedded market’s needs for a simple, affordable solution to make use of modern SSDs. Zynq SSE is a fully integrated and pre-validated subsystem stack comprising 3rd-party SATA Host Controller and DMA IP cores from ASICS World Services, a storage micro-architecture from MLE, Xilinx PetaLinux, and an Open Source SATA Host Controller Linux kernel driver, also from MLE. Zynq SSE utilizes the Xilinx GTX Multi-Gigabit Transceivers to integrate physical SATA connectivity.

Key Features of ZYNQ SATA Storage Extension (SSE)

- Provides one single SATA host port for HDD or SSD connectivity

- Compatible with SATA I (1.5 Gbps), SATA II (3 Gbps) and SATA III (6 Gbps) speeds

- Access via a standard Linux block device interface and Linux filesystems

- Fully integrated and tested SATA Host Controller IP Core

- Fully integrated and tested DMA Controller IP Core

- SATA driver for Linux/Petalinux available in binary and open source

- Less than 3% resource utilization on a Zynq 7045 leaves more than 95% of Zynq resources for you

Core Benefits

- Reduce PCB footprint and BoM costs with this integrated FPGA solution

- Reduce development cost, time and risks with this integrated, pre-validated system stack

- Enables tight storage algorithm integration and test for de-duplification, scrubbing, compression, etc.

Applications

- Cost efficient, fast and reliable storage solutions for Embedded Systems

- Supervisory, Control and Data Acquisition (SCADA) systems

- Smart Storage, Software-defined Storage, Network-Attached Storage (NAS)

- Storage and Retrieval for Test & Measurement

- Video Imaging Record and Replay

Pricing

MLE’s license fee structure reflects the needs of Zynq’s Embedded Linux users for simple and affordable SATA with optional upgrade paths.

| Product Name | Deliverables | Pricing |

|---|---|---|

|

Evaluation Reference Design (Zynq SSE ERD) |

Binary-only system stack. Zynq PS / Linux software-only SATA API. Tried and tested to work on the Avnet Zynq Mini-ITX Boards 7Z045 and 7Z100 only. Evaluation-only license. |

free of charge |

|

Production Reference Design – Experts Edition (Zynq SSE PRD-EE) |

Complete, downloadable SATA-I/II/III system stack and Vivado 2016.4 design project with encrypted RTL code. Zynq PS / Linux software-only SATA API. (Same as Zynq SSE ERD) Production-ready: Pre-integrated and tested to be portable to Your target system hardware. Fully paid-up for, royalty-free, world-wide, Single-Project-Use License, synthesizable for 1 year. Bug-fixes only with basic support via email. |

$9,800.- |

|

Production Reference Design – Professional Edition (Zynq SSE PRD-PE) |

Complete, downloadable SATA-I/II/III system stack and Vivado 2016.4 design project with encrypted RTL code. Zynq PS / Linux software-only SATA API. (Same as Zynq SSE ERD) Production-ready: Pre-integrated and tested to be portable to Your target system hardware. Fully paid-up for, royalty-free, world-wide, Single-Project-Use License, synthesizable for 1 year. Up to 40 hours of premium support and integration design services via email, phone or online collaboration. |

$14,800.- |

|

Other SATA-I/II/III Offerings |

Multiple SATA host ports, PL-connected SATA host ports, Multi-Project-Use Licenses, RTL Source Code Licenses, other FPGA devices than Zynq, etc. Classical IP core licenses with annual maintenance, project-specific support and integration design service packages, etc. |

Starting at $19,800.- |

On the technical side, all Zynq SSE offerings implement one single SATA-I/II/III host operating the Xilinx GTX multi-gigabit transceivers at 1.5 or 3.0 or 6.0 Gbps and making use of modern SSDs Native Command Queueing (NCQ), Scatter-Gather Direct Memory Access (SG-DMA), Linux kernel drivers and Linux device tree. SATA API via a standard Linux block device from Linux user-space software.

And yes, the license fee for the Production Reference Designs includes a fully paid-up for, royalty-free, world-wide, Single-Project-Use license for a single instance of the SATA Host Controller and DMA IP cores from ASICS World Services, the FPGA storage micro-architecture from MLE, and MLE’s SATA Host Controller Linux kernel driver.

Documentation

- ZYNQ SATA Storage Extension for the Xilinx ZC706

- ZYNQ SATA Storage Extension (SSE) – Benchmark for the Xilinx ZC706

- ZYNQ SATA Storage Extension for the Avnet Mini-ITX

- ZYNQ SATA Storage Extension (SSE) – Benchmark for the Avnet Mini-ITX

- ZYNQ SATA Storage Extension (SSE) for Network-Attached Storage (NAS) for the Avnet Mini-ITX

- ZYNQ SATA Storage Extension (SSE) for Network-Attached Storage (NAS) for the Xilinx ZC706

- How to setup an evaluation of ZynqSSE

- How to do performance benchmarking of ZynqSSE

- How to develop your next embedded system with the complete design user guide for the Production Reference Design of Zynq SSE

Frequently Asked Questions

What is ZYNQ SATA Storage Extension (SSE)?

Zynq SSE is a turnkey solution and reference design which we intend as one single plug & play SATA host port add-on for Xilinx Zynq when running under Linux.

Is ZYNQ SATA Storage Extension (SSE) an IP Core?

While Zynq SSE instantiates IP cores, namely the full ASICS.WS SATA Host Controller and DMA Controller, it is not a soft FPGA IP Core by itself.

Zynq SSE is closer to the other hard IP core I/O functions inside the Zynq Processing System (PS), like UART or SDIO: It is fully instantiated and ‘frozen’ and cannot be altered – other than you are able to change the pin assignment.

How many SATA ports does ZYNQ SATA Storage Extension (SSE) Support?

Zynq SSE supports one (and only one) single SATA Host Port. If you need more, please contact us to discuss other possible solutions. There are several!

I need more than one SATA Port, what shall I do?

Based on our experiences with Xilinx Zynq and SATA, a typical multi-host SATA system comes with certain performance requirements, which most often lean towards an application-specific architecture to deliver such performance.

So, honestly, Zynq SSE cannot do that!

However, we see a couple of options, depending on your project’s needs: For example, we can design for you a special multi-host reference design. Or, we can assist you in purchasing the ASICS.WS SATA Host Controller and DMA IP Core.

Please contact us directly to discuss your options.

What is an ERD?

ERD means Evaluation Reference Design. This is a complete compilable Vivado design project comprising an encrypted netlist of the MLE storage micro-architecture, plus all precompiled images, ready-to-run. ERD is a fully functional SATA host which runs for at least 12 hours, until it then times-out. You can request download instructions for an ERD from MLEcorp.com for testing, free-of-charge.

What is a PRD?

PRD means Production Reference Design which comes in two forms, a PRD-3G for SATA-II and a PRD-6G for SATA-III with support for FPDMA and NCQ. PRD is a Vivado design project comprising an encrypted netlist of the MLE storage micro-architecture. A PRD must be purchased from MLEcorp.com which gives you the rights to take Zynq SSE into production for one single named project.

I want to evaluate ZYNQ SATA Storage Extension (SSE), what is the easiest way?

The easiest way is to use the ERD for the Avnet mini-ITX Board which has a SATA header on board. The ERD comes with precompiled binaries. You can request a free-of-charge download from the Request Form on this page.

I want to evaluate ZYNQ SATA Storage Extension (SSE) on my own target hardware board, is that possible?

Yes, please contact us and request download instructions for an ERD. ERD comes with a full Vivado design project for you to retarget to and test on your hardware. Please refer to the Zynq SSE Developers Guide of the ERD on how to re-compile. The Developers Guide will also provide information for the SATA capable reference clock to the GTX Clock input (150 MHz, low jitter).

Do I need a License Key for ERD?

No, you will not need any License Key in order to run, or to re-compile, the Zynq SSE ERD.

Do I need a License Key for PRD?

Yes, you will need two License Keys, a Compile-time License Key, and a Run-time License Key:

- The Compile-time License Key is a Vivado Flex License Key file, tied to the host ID of your design workstation. With this key you can compile the Zynq SSE reference design to add your own design portions, change the SATA pin-out, and to generate bitfiles. We will send you one Compile-time License Key after proof-of-purchase.

- The Run-time License Key is specific to your Zynq SSE and will disable the time-out mechanism. We will send you one Run-time License Key after proof-of-payment. Please follow the instructions in the MLE Zynq SSE Developers Guide to add this key file to the Linux root filesystem of your Zynq system.

How long will the License Keys be active?

The Compile-time License Key will expire one year after the purchase date. This should be plenty to finish off your design project. The Run-time License Key will never expire.

What does a ZYNQ SATA Storage Extension (SSE) PRD include?

Each PRD contains everything you need to extend your Zynq system insert with one single SATA host port: This includes documentation – the so-called Developer’s Guide – and a Vivado design project with the ASICS.WS SATA Host Controller and DMA IP-Core inside the MLE microarchitecture and the Linux device drivers. Plus, all the (legal) rights to put those into production for your single, named project.

How much support do I get?

You will receive all reasonable support, typically via Email.

For full functionality of ZYNQ SATA Storage Extension (SSE), do I have to purchase any other licenses?

No. Once you purchase a PRD you will get the Compile-time Key and the Run-time Key to design-in and to operate a fully functional SATA host on Zynq. Our invoice together with the MLE Product License Agreement gives you the legal rights to make and use Zynq SSE for one single named project.

What documentation exists for ZYNQ SATA Storage Extension (SSE)?

Besides the online documentation listed on our website, as part of each ERD or PRD you will receive a complete developers guide which explains how to design-in Zynq SSE into your project.

What do you mean with Single-Project-Use?

Without being legalistic here, the single-project-use license allows you use Zynq SSE within the same design project. If you need to fix errors within the FPGA design, or the PCB, and ship a new revision, that would be considered the same project. If you change the device package or re-design the PCB that would probably be another design project. We suggest to follow Xilinx’ concept for project based licensing. Please do not hesitate to contact us if you need clarification.

How long does the PRD work without a Run-time License Key?

Without a purchased Run-time License Key, the SATA link in the PRD will disconnect after 12 hours. Once you have installed the Run-time License Key, this time-out will be disabled.

Does the PRD-3G/6G (with or without a Run-time License Key) have any speed limitations?

No, the PRDs come with full functionality for SATA-II, or SATA-III, respectively.

I have purchased a ZYNQ SATA Storage Extension (SSE) PRD-3G, is it possible to upgrade to PRD-6G?

Yes, as long as you have a valid Compile-time License Key, you can upgrade from SATA-II to SATA-III. We will apply the payment for PRD-3G towards your payment of PRD-6G.

How can ZYNQ SATA Storage Extension (SSE) be priced lower than what a typical SATA IP core costs?

The reason for pricing Zynq SSE is to reflect the needs of Zynq users who look for connectivity solutions, but not necessarily a full soft FPGA IP core as such:

In general, the advantage of an IP core is that you can instantiate it freely in your design. You can parameterize and change and instantiate the IP core in many ways and as many times as needed. If you purchased the RTL source code version, you could even change the functionality. The drawback is the cost (and time) of integrating an IP core and the effort you have to put into driver development. And, sometimes, there is a support burdon for the IP core vendor, too.

Zynq SSE is a turnkey reference design where the underlying IP core has been ‘frozen’. You can instantiate it exactly once (and only once) per device. By integrating this with Linux – including Linux device drivers – and making this available for Zynq-only we are able to come up with a great price for a Single-Project-Use license.

We believe that this model has many advantages for all parties involved.

Can I use ZYNQ SATA Storage Extension (SSE) without Linux?

No, Zynq SSE is technically and license-wise bundled with Zynq and Linux. However, we can support your project with a SATA IP core from ASICS.WS. Please read below and/or contact us.

Which Linux can I use?

We have extensively tested Zynq SSE for Xilinx PetaLinux 2013.04. You can download this from the following git repository:

https://github.com/Xilinx/linux-xlnx/branches

In general, there is no reason why Zynq SSE should not work with other Linux Kernel versions applicable to Zynq.

What SATA performance will I see with ZYNQ SATA Storage Extension (SSE)?

We took a conservative stand when we parameterized Zynq SSE. Key objective was to make it robust and work in almost all user cases. This limits the raw speed to approximately 200MB/sec for the PRD-3G. When we say ‘raw speed’ this is to and from the SATA Linux block device (a.k.a. /dev/sdX) without Linux filesystem layers involved. Obviously, filesystem handling adds to the processing burdon which leads to lower read/write speeds.

What if I need higher SATA performance than ZYNQ SATA Storage Extension (SSE) offers?

If you need more performance than the raw speed to approximately 200MB/sec for the PRD-3, for example to max-out your super-fast SSD we believe we can help you. We are prepared to discuss with you acceleration options like bypassing the Linux system by writing directly into the SATA device, or other protocol acceleration techniques we have been working on. Just contact us directly!

Can I buy a SATA IP Core from MLE?

We would be more than happy to directly assist you in selecting and purchasing the right variant of a SATA IP Core from ASICS.WS. ASICS.WS has prepared us to discuss with you pricing and licensing options, or, for example, whether you should get HDL source code or just a netlist, or an evaluation, a single-project-use or a multi-project-use license.

And, obviously, we do know the ASICS.WS SATA Host Controller and DMA IP Core in-and-out. So you can ask us technical questions, too!

Can I buy a full turnkey system with hardware (PCB) and software from MLE?

Sure, we have done turnkey solutions in the past and will be happy to discuss details with you, including PCB design and manufacturing.

Do you provide more detailed information about the device utilization?

You can either download and compile the ERD for your target device and look at your Vivado utilization report. Or, below are the most important sections of the utilization report for a XC7Z100 device:

| Slice Logic | ||||||

| Site Type | Used | Loced | Available | Util% | ||

| Slice LUTs | 5922 | 0 | 277400 | 2.13 | ||

| LUT as Logic | 5794 | 0 | 277400 | 2.08 | ||

| LUT as Memory | 128 | 0 | 108200 | 0.11 | ||

| LUT as Distributed RAM | 10 | 0 | ||||

| LUT as Shift Register | 118 | 0 | ||||

| Slice Registers | 4623 | 0 | 554800 | 0.83 | ||

| Register as Flip Flop | 4623 | 0 | 554800 | 0.83 | ||

| Register as Latch | 0 | 0 | 554800 | 0 | ||

| F7 Muxes | 35 | 0 | 138700 | 0.02 | ||

| F8 Muxes | 2 | 0 | 69350 | <0.01 | ||

| Memory | ||||||

| Site Type | Used | Loced | Available | Util% | ||

| Block RAM Tile | 3 | 0 | 755 | 0.39 | ||

| RAMB36/FIFO* | 3 | 0 | 755 | 0.39 | ||

| FIFO18E1 only | 1 | |||||

| RAMB36E1 only | 2 | |||||

| RAMB18 | 1 | 0 | 1510 | 0.06 | ||

| RAMB18E1 only | 1 | |||||

| * Note: Each Block RAM Tile only has one FIFO logic available and therefore can accommodate only one FIFO36E1 or one FIFO18E1. However, if a FIFO18E1 occupies a Block RAM Tile, that tile can still accommodate a RAMB18E1 | ||||||

| Clocking | ||||||

| Site Type | Used | Loced | Available | Util% | ||

| BUFGCTRL | 8 | 0 | 32 | 25 | ||

| BUFIO | 0 | 0 | 32 | 0 | ||

| MMCME2_ADV | 2 | 0 | 8 | 25 | ||

| PLLE2_ADV | 0 | 0 | 8 | 0 | ||

| BUFMRCE | 0 | 0 | 16 | 0 | ||

| BUFHCE | 0 | 0 | 168 | 0 | ||

| BUFR | 0 | 0 | 32 | 0 | ||